在过往,在很多关于芯片的文章中,相信你应该见过了不少的概念科普。但这篇应该是你从来都没有看过的硬核科普。该篇文章的作者从原理出发,抽丝剥茧地介绍每一个概念,帮助大家去了解不同的概念。

以下为文章全文:

ALUs和CPUs

最近我一直在思考这个问题,下文是我的解释。计算机的核心是一个称为算术逻辑单元(ALU)的功能块。毫不奇怪,这是执行算术和逻辑运算的地方,比如算术上两个数字相加求和、逻辑上两个数值进行“与”运算。

算术逻辑单元(ALU)是计算机的核心(图片来源:Max Maxfield)

请注意,我没有用任意形状表示ALU,这种‘Y’字形是工程师通常使用的符号,因为ALU接受两个输入值并返回一个输出。

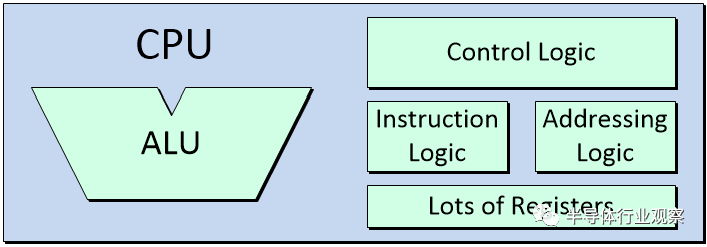

当我们将ALU与一系列寄存器(另请参阅“寄存器vs锁存器vs触发器”)、一些指令逻辑、一些寻址逻辑和一些控制逻辑结合在一起使用时,我们最终会得到一个中央处理器(CPU)。请注意,在这种情况下,当我们说“逻辑”时,我们指的是用于形成数字电子系统的原始逻辑门和寄存器元件。

中央处理器(CPU)是计算机的大脑(图片来源:Max Maxfield)

中央处理器负责通过执行由指令指定的算术、逻辑、控制和输入/输出(I/O)操作来执行形成计算机程序的指令。

内存和CPU—内存体系结构

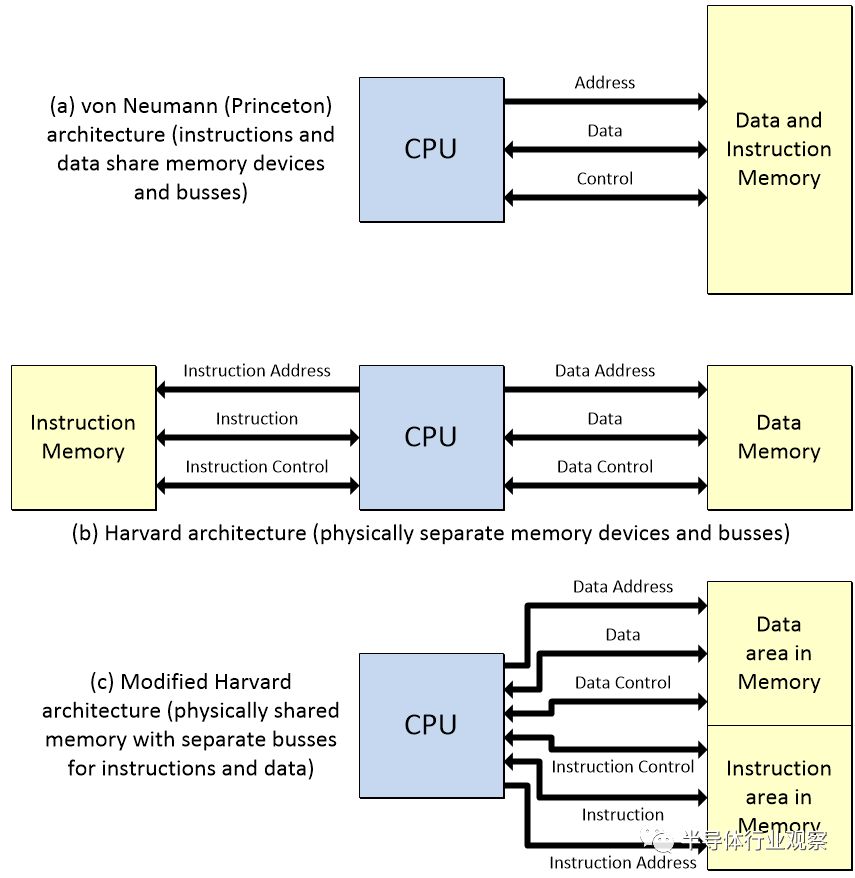

为了让CPU发挥魔力,它需要访问用于存储指令和数据的内存子系统。这就是事情变得有点棘手的地方,因为有两种基本的计算机体系结构,称为冯·诺伊曼(或普林斯顿)体系结构和哈佛体系结构。

在冯·诺伊曼/普林斯顿体系结构中,数据和指令都存储在相同的物理存储空间中,并使用相同的地址、数据和控制总线进行访问。相比之下,在哈佛体系结构中,指令和数据存储在物理上不同的存储器件中,使用它们自己的总线进行访问。

基本计算机体系结构:冯·诺依曼/普林斯顿、哈佛和改良哈佛(图片来源:Max Maxfield)

还有一种风格称为“改良哈佛体系结构”,其中指令和数据共享相同的物理存储器件,但是使用它们自己的总线进行访问(特殊的机制可以防止指令被误认为数据,反之亦然)。

在接下来的讨论中,我们将重点讨论冯·诺依曼/普林斯顿架构(因为它对我来说更容易画),但是我们讨论的所有内容都适用于所有三种体系结构。

有缓存吗?

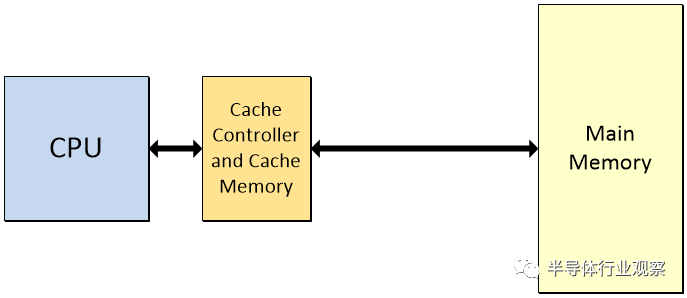

计算机的一个问题是,指令和数据在主存储器和CPU之间来回传递需要相对较长的时间。问题是,绝大多数的程序都包含大量的小循环,在这些小循环中,相同的操作被一次又一次地执行。解决方案是创建一个(相对)较小的高速内存,称为高速缓存,以及一个特殊的高速缓存控制器,它位于CPU附近,保存经常访问的指令和数据的副本。

高速缓存是一个(相对)小的高速内存,位于CPU附近(图像来源:Max Maxfield)

请注意,上图是一个粗略的简化图。现代处理器有独立的指令和数据缓存。此外,还有一个称为L1、L2、L3等的缓存层次结构。(其中“L”代表“Level”,即级别)。L1缓存是最小、最快、最靠近CPU的缓存。

系统设计人员必须考虑的一个问题是,确保CPU对缓存内容所做的任何更改随后都反映在主内存中(如果合适的话)。同步缓存和主内存的内容,同时保持这些内容的完整性是一项极其复杂的任务,因此你会很高兴地发现,我们在这里将不再进一步讨论它。

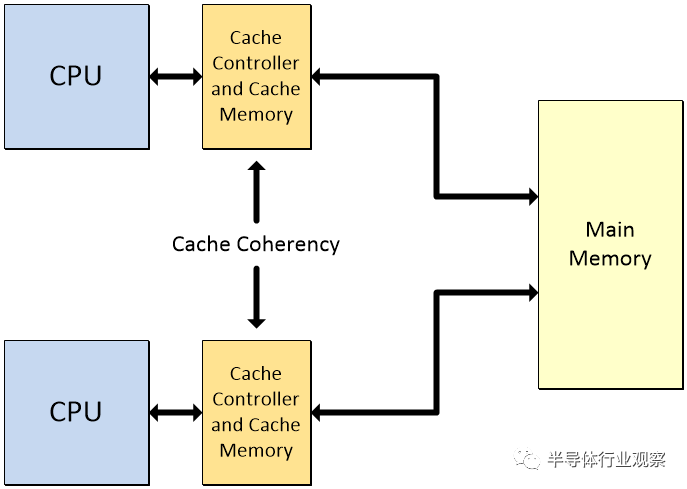

然而,我们必须提的一件事是缓存一致性,它在拥有多个CPU(每个CPU都有自己的高速缓存子系统)共享公共内存资源的系统中开始显露出问题。

当多个CPU共享公共内存资源时可能会出现问题(图片来源:Max Maxfield)

正如维基百科告诉我们的:“在一个共享内存多处理器系统中,每个处理器都有一个单独的高速缓存,因此可能有多个共享数据副本:一个副本在主存储器中,一个副本在请求它的每个处理器的本地高速缓存中。当数据的一个副本发生更改时,其他副本必须反映这个更改。缓存一致性是确保共享操作数(数据)值的变化在整个系统中及时传播的规则。”我自己说得再好不过了。

添加FPU

早期的CPU使用重复加法进行整数乘法运算。他们还使用了非常复杂的技术来进行整数除法运算。(另请参阅“计算机如何进行数学运算”)。没过多久,设计师就开始添加特殊的乘法器/除法器功能。

类似地,许多早期的CPU被设计为执行定点算术运算。当涉及到更复杂的浮点运算时,这些是通过将浮点运算分解成更简单的运算序列并使用定点架构来执行这些运算来实现的。

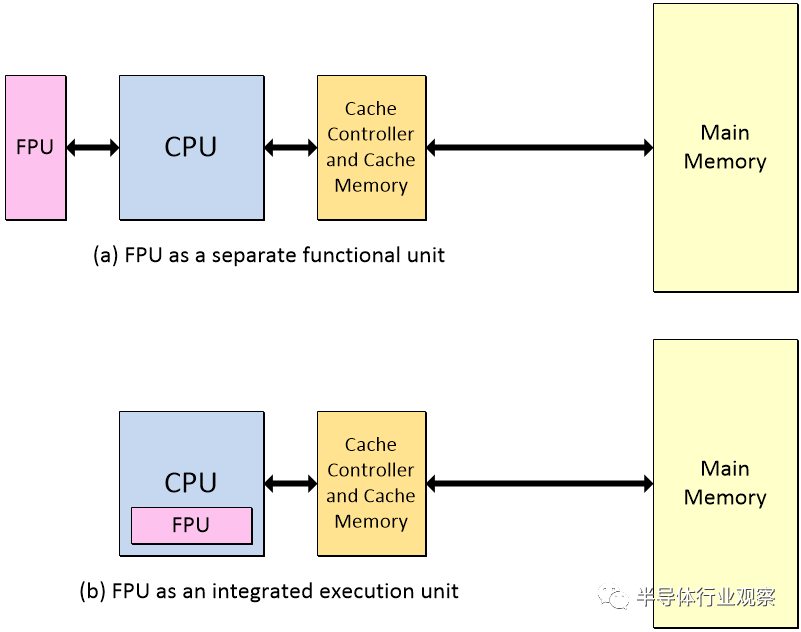

随着人们越来越多地使用计算机,人们希望自己的计算机运行得越来越快,实现这一点的一种方法是添加一个特殊的浮点运算单元(FPU)。FPU的作用是对浮点数执行加、减、乘、除、平方根和移位操作。

FPU对浮点数进行运算(图片来源:Max Maxfield)

FPU作为一个单独的功能单元来实现是很常见的,但将一个或多个FPU集成为CPU中的特殊执行单元也并不少见。

内存保护和管理:MPUs和MMUs

内存保护单元允许特权软件(如操作系统)定义内存中的区域,并为这些区域分配访问权限和属性。

添加内存保护单元(MPU)(图片来源:Max Maxfield)

MPU监视CPU和内存之间的事务,并在检测到访问违规时发出警报(触发故障异常)。MPU的主要目的是防止程序访问没有分配给它的内存。这可以防止普通程序或恶意软件程序中的无辜错误影响其他进程或操作系统本身。

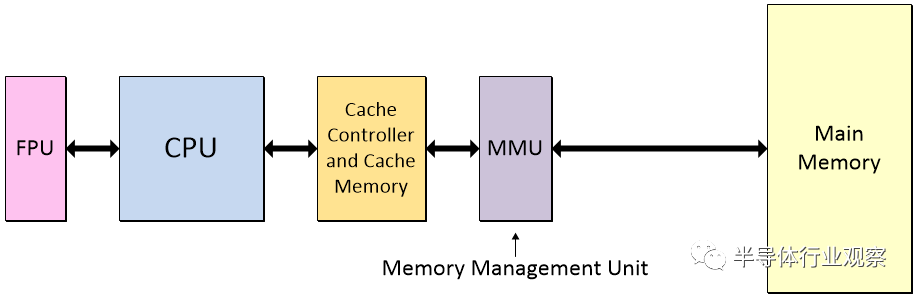

层次结构的下一步是使用内存管理单元(MMU),它通过附加功能增强了内存保护单元(MPU)的功能。

将内存保护单元升级为内存管理单元(MMU)(图片来源:Max Maxfield)

这就是事情开始变得有点棘手的地方。最简单的级别是在“裸机”上运行单个程序,裸机指的是计算机直接在中央处理器上执行程序,没有中间的操作系统。在这种情况下,可以使用绝对(物理)地址编译程序。

更复杂的系统运行一种叫做操作系统(OS)的特殊程序。操作系统允许用户同时运行多个程序。以你自己的个人计算机为例,你可能在计算机上同时运行文字处理程序、图像程序和电子邮件程序。其工作方式是使用相对寻址来编译这些程序。MMU的任务是将程序中的虚拟地址转换成主内存中的物理地址。

请注意,由于MMU包含了MPU的功能,因此它们是相互排斥的——一个系统可以有MMU,也可以有MPU(或两个都没有),但不能同时有两个。

微处理器和微控制器

如今,当我们使用“计算机”一词时,大多数人(非工程师)通常会想到他们的台式机、笔记本电脑或平板电脑。相比之下,根据不同的领域,工程师可能会想到工作站或服务器,或想到微处理器和微控制器。

然而,在我们开始讨论微处理器和微控制器之前,我们应该注意,上面讨论的所有概念一般都适用于计算机体系结构。例如,大约在20世纪60年代早期的计算机是由一屋子的被称为“大型机”的大柜子组成的。每个机柜都有不同的功能,比如CPU或主存储器。通俗地说,这种类型的计算机被称为“大铁”机器。

大约在20世纪70年代作为集成电路(“芯片”)实现的第一批CPU被称为微处理器(µP)。后来,它们开始被称为微处理器/微处理单元(MPU)。如今,µP和MPU被认为是同义词。

早期的MPU仅包含CPU。诸如浮点运算单元(FPU,也称为数学协处理器)和内存保护单元(MPU)或内存管理单元(MMU)之类的功能是在单独的器件上实现的,所有这些器件都紧密地安装在印刷电路板上。

当然,使用MPU这三个字母代表同时微处理器单元和记忆保护单元只会增加乐趣和误会,但你通常可以从谈话的上下文中看出人们在说什么(如果没有,那就让他们先把事情说清楚,然后再掏钱)。

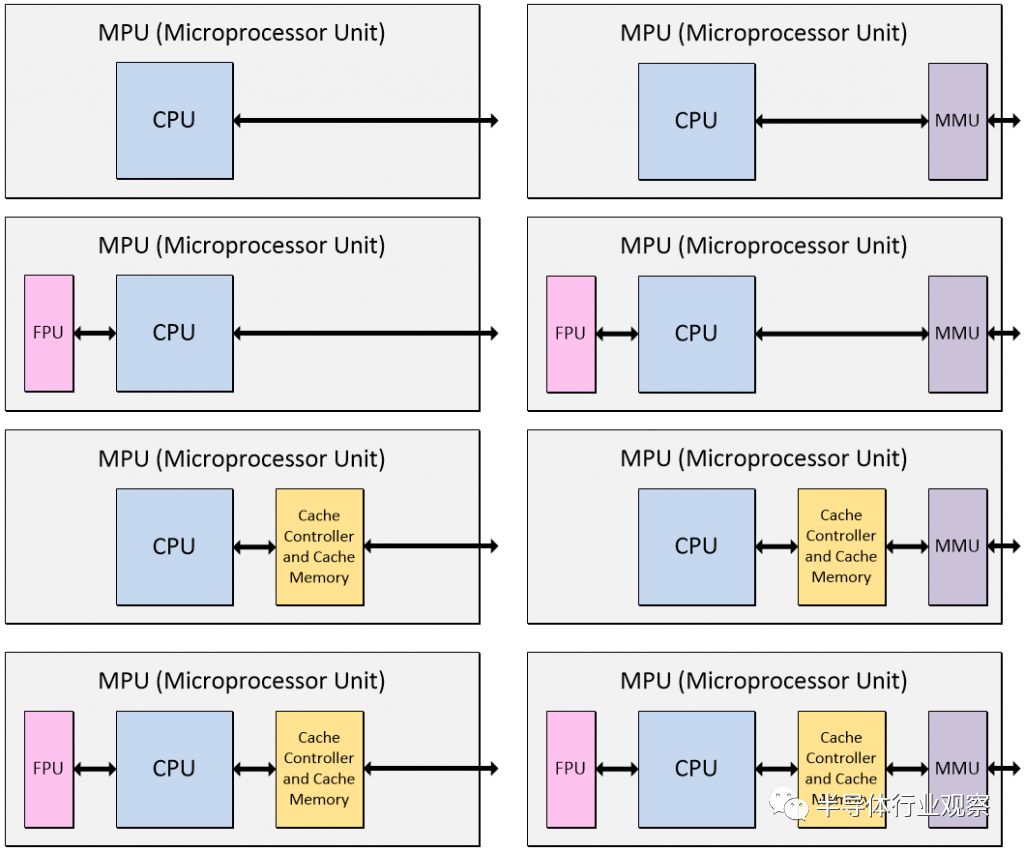

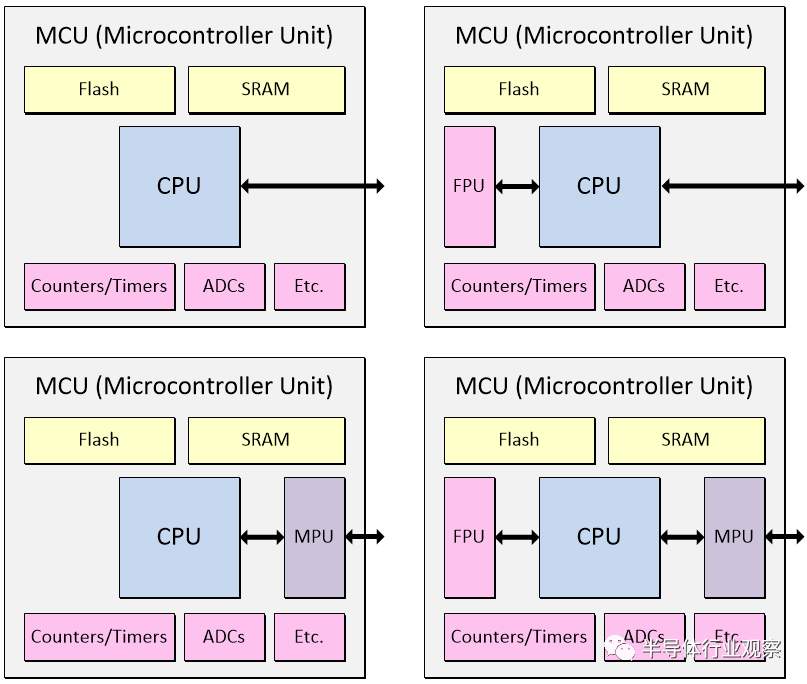

这些天,有成千上万的MPU产品。一些只包含一个单独的CPU,一些包含一个CPU以及缓存、FPU和内存保护或内存管理单元的各种组合,还有一些包含多个CPU、FPU等。(请注意,MPU可能包含额外功能——出于讨论的目的,我们将重点放在核心功能上。)

微处理器单元(MPU)有多种形状、大小和配置(图片来源:Max Maxfield)

与内存管理单元(MMU)相反,一些微处理器单元(MPU)可能包含内存保护单元(MPU),但是为了避免混淆,我们在这里写出了全名。此外,根据经验,更常见的是在微处理器中找到内存管理单元,在微控制器中找到内存保护单元,如下所述。

微处理器的一个显著特点是它不包含任何内存(不包括任何缓存)。也就是说,它的所有内存都是器件外部提供的。相比之下,微控制器(µC,也称为微控制器单元,MCU)包含的存储器包括Flash形式的非易失性程序存储器(NVM)和SRAM形式的易失性工作存储器。MCU通常包含各种附加功能和能力,包括计数器和定时器,以及带有模数转换器(ADC)的模拟输入。

微控制器单元(MCU)有多种形状、大小和配置(图片来源:Max Maxfield)

MCU通常不包含任何高速缓存存储器的一个原因是它们经常必须提供实时控制功能和性能。这可能涉及运行“裸机”程序——或者在内核或实时操作系统(RTOS)下运行程序——而拥有缓存内存子系统往往会扼杀确定性。

此外,微处理器通常不运行像Linux或Unix这样的复杂操作系统,因此不需要内存管理单元(MMU)。如果它们有内存保护的话,也通常不会比内存保护单元(MPU)更复杂。同样,MCU可能包含额外的功能——出于讨论的目的,我们将重点放在核心功能上。

图形处理单元(GPUs)

最后,但同样重要的是,在本专栏中,我们会讨论图形处理单元(GPU)。虽然微处理器单元(MPU)仅包含几个(例如,1个、2个、4个或8个)复杂的CPU内核,但GPU可以包含数百或数千个较简单的CPU核心,每个CPU核心具有少量的本地存储器,以及FPU等。

顾名思义,GPU最初是为图形应用程序设计的,在图形应用中,需要在屏幕上对数十万或数百万像素执行相同的操作。但是,GPU还可以在受益于大规模并行处理的应用程序中使用,包括硬件加速,网络货币(“比特币”)挖掘和高性能计算(HPC)。

MPU(微处理器)和GPU组合可以在手机、笔记本电脑、平板电脑、工作站和游戏机等系统中找到。同时,在嵌入式系统中可能会发现MCU(微控制器)和GPU组合。

模拟、数字、混合信号和RF ASICs

以术语ASIC为例。当你听到或看到这个词时,你会想到什么?如果你的下意识反应是说ASIC指的是一种定制的数字集成电路,包含数十万、数百万甚至数十亿个晶体管,那么这可能意味着你来自数字背景。

让我们从ASIC代表特定应用集成电路的事实开始,即为执行特定任务而创建的自定义器件。在这个标题中,我们看不到“数字”这个词。同样值得提醒自己的是,没有所谓的模拟晶体管或数字晶体管——只有晶体管可以认为是在模拟域(信号在一个连续的范围内工作)或数字域(信号在一定数量的定义电平下工作)中发挥它们的魔力。

在现实中,我们可以创建包含晶体管和其他组件的模拟ASIC,以实现类似放大器或滤波器的模拟功能。这种器件通常只包含相对较少的晶体管(数量在几十、几百或几千个),而且这些晶体管通常体积大而坚固,它们的形状和大小都经过了微调,以满足严格的规格要求。(我们所说的“大”指的是“在事物的体系中”,与用来制造数字集成电路的晶体管相比——它们在人类存在的尺度上仍然小得令人难以置信。)

我们也有可能创造出包含晶体管和其他元件的数字专用集成电路,以实现一系列的数字功能。这类器件通常包含相对大量的晶体管(以数十万、数百万或数十亿计),而这些晶体管通常体积小、活跃、非常集中。

如果我们能把世界分成模拟和数字两部分,生活就会变得如此简单,但是,情况无疑会更复杂,因为许多ASIC包含模拟和数字功能的混合,因此被称为混合信号器件。这类元件的典型例子是模数转换器(ADC)和数模转换器(DAC)。在现实中,即使是你可能认为是“纯数字”的器件,也可能仍然包含一些以锁相环(PLL)等功能形式存在的少量模拟功能。

而且,仅仅为了增加乐趣,还可以有射频(RF)ASIC,有些人将其称为射频集成电路(RFIC)。

ASICs与ASSPs

一般而言,专用集成电路(ASIC)是由单个公司在特定系统中设计和/或使用的组件。相比之下,专用标准部件(ASSP)是一种更通用的器件,旨在供多个系统中的多个系统设计机构使用(例如USB接口芯片)。这就引出了一个有趣的问题——我们是将ASIC和ASSP视为在模拟、数字、混合信号和RF之下(图1a),还是将其看作相反的情况(图1b)?

图1 ASIC和ASSP器件与模拟、数字、混合信号和RF领域的关系是什么样的?(图片来源:Max Maxfield)

在现实中(我不得不停止这样说),这些术语都只是我们为自己创造的“盒子”,但反思一下不同的人以不同的方式思考这些事情仍然很有趣。(如果你愿意在下面的评论中分享你更喜欢哪种表达方式,那就太好了。)

每个实现域(模拟、数字等)通常基于自己的专用半导体衬底和工艺,并且每个开发团队通常使用他们自己的专用设计、验证和分析工具。

为了进行这些讨论,我们假设我们谈论的是数字ASIC和ASSP。此处要理解的关键点是,这些器件是使用相同的设计、验证和分析工具开发的,而且是使用相同的半导体工艺和技术实现的。

ASIC与ASSP的惟一区别在于它的目标受众和部署——特定系统(或系统系列)中的单个公司vs各类系统中的多个公司。我们甚至可以说,一个在早上被认为是ASIC的器件,如果它的主人决定与世界分享,那么它就可以在下午被改造成ASSP。

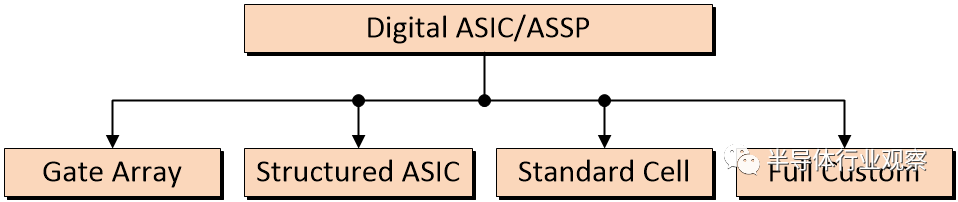

我们要说最后一点是,数字ASIC(或ASSP)有不同类型。就日益增加的复杂性而言,它们将被分为门阵列、结构化ASIC、标准单元和全定制。

图2.不同风格的数字ASIC/ASSP(图片来源:Max Maxfield)

你会高兴地发现,我们不会在这个泥潭里挖得更深。我只想说,如果你想了解更多关于这些家伙的信息,我的书《Bebop to the Boolean Boogie》(世界上第一本也是唯一一本以海鲜秋葵汤食谱为特色的电子学书籍)对它们进行了极其详细的讨论。

MPUs、MCUs、DSPs、FPGA和内存器件

莎士比亚表现出了他一贯的先见之明,当他让李尔王说:“哦,那是疯狂的谎言。”我很肯定他在想,如果人们开始尝试把微处理器(MPU)、微控制器(MCU)、数字信号处理器(DSP)、现场可编程门阵列(FPGA)和内存器件(DRAM、SRAM、Flash等)分成ASIC和ASSP会如何。

不幸的是,如果你不小心,你会发现自己拼命地想要把一颗方钉子钉进一个圆孔里。就我个人而言,我花在这款游戏上的时间远远超过了应该花的时间。多年来,我已经得出结论,说“MPU就是MPU”、“SRAM内存芯片只是SRAM内存芯片芯片”更容易,就这样吧。

片上系统(SoC)器件

片上系统(SoC)是指充当整个子系统的ASIC或ASSP。除了一堆定制功能块(其中大多数通常是数字的,但也可以包括一些模拟和/或混合信号功能),SoC还包括一个或多个处理器内核(处理器和/或DSP)、辅助内核(例如FPU、计数器/定时器)、片上存储器和外围/通信内核/功能。

有些人认为SoC比ASIC/ASSP“更高”,因为它们是基于ASIC/ASSP技术加上处理器核心等。相比之下,在并非所有ASIC/ASSP都包含处理器内核的基础上,其他人则认为ASIC/ASSP技术是父项,而SoC构成了这些器件的子集。

再说一次,这些术语都是我们为自己创造的“盒子”,但反映出不同的人以不同的方式思考这些事情仍然很有趣。

2.5D和3D ICs

最初,在集成电路的背景下,人们对于2.5D和3D有很多混淆。很多这种困惑是由公司造成的,他们有我们现在认为是2.5D IC的东西,而在他们的营销文案中则声称是3D IC(小小的骗局)。

每个未封装的集成电路称为裸片。在2.5D IC的情况下,多个裸片安装在称为硅插入器的基础层上。硅插入器及其所附的裸片全部呈现在单个封装中。硅插入器用于将芯片相互连接,也可连接到封装的端子(引脚或焊盘)。

在3D IC的情况下,多个裸片彼此堆叠,并使用硅通孔(TSV)进行连接。单个多裸片堆叠可以以其自己的封装呈现,或者多个多裸片堆叠可以安装在硅插入器上,而整个组件以单个封装呈现。

SiPs、PiPs、PoPs和MCMs

多芯片组件(MCM)在概念上类似于2.5D IC,安装裸片和其他组件的统一高密度互连(HDI)基板不同于硅插入器,范围从陶瓷到印刷电路板(PCB)。

顺便说一句,组成MCM的单个裸片被称为“chiplet”。一切都放在一个单独的封装中,这意味着MCM在外界看来就像一个大型IC。

根据设计的复杂性和目标应用程序和/或环境的不同,MCM有多种风格。它们通常分为MCM-L(基板是多层层压PCB)、MCM-D(组件使用薄膜技术沉积在基板上)和MCM-C(基板是陶瓷)。

术语System-in-Package(Sip)对不同的人意味着不同的事情。有些人认为SiP只是MCM的一个更现代和新潮的名字。其他人则认为SiP介于MCM(因为SiP的裸片可能堆叠在彼此的顶部)和3D IC之间(因为SiP不使用最高级别的TSV互连,而这正是3D IC的特点)。

到头来,SiP需要将多个裸片和其他组件安装在同一块基板(通常是HDI PCB)上,并作为单个封装呈现给外界。

最后,但同样重要的是,对于我们讨论的这一部分,我们有Package-in-Package(PiP)和Package-on-Package(PoP)。多个裸片(每个裸片在它们自己的芯片级封装(CSp))和/或SiP被安装、连接,并作为单个封装呈现给外界。相比之下,在PoP组件的情况下,两个或更多的封装安装在彼此的顶部,它们之间有一个接口来路由信号。所有这些技术都允许在移动电话、个人数字助理(PDA)、平板电脑、数码相机等产品中实现更高的组件密度。

COMs和SOMs

遗憾的是,术语嵌入式模块计算机(COM)和系统模块(SOM)同样有多种解释。

一种非常常见的解释是将系统的所有功能集成在单个模块上的PCB级电路(与SoC相反,SoC必须安装在电路板上,并且通常依赖于诸如存储器器件的外部组件来完成系统)。

为了更好地理解COMs/SOMs的这种解释,请参考来自Toradex的Apalis Arm家族COM和Colibri Arm家族SOM。此外,请参考我的专栏《COM-HPC为边缘计算定义服务器级功能》。

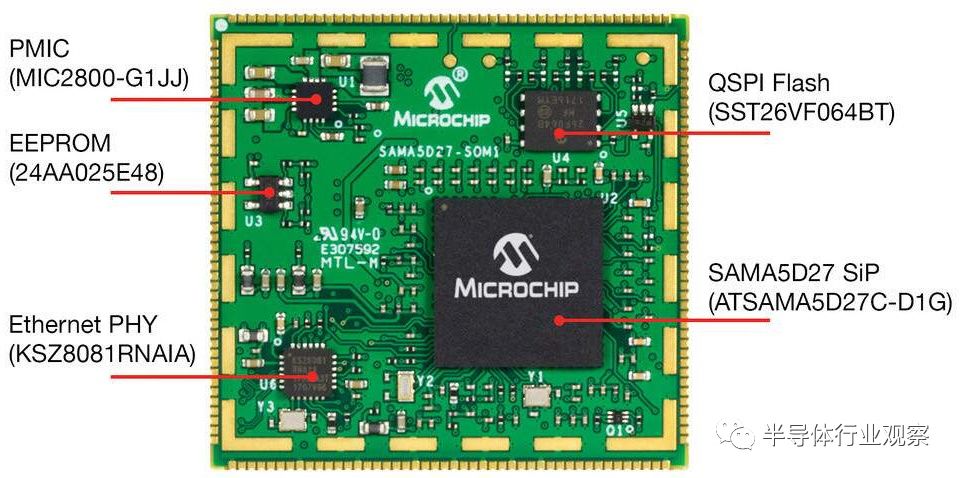

另一种解释是SOM不大于大型IC。这种解释的一个经典例子是Microchip Technology的SAMA5D27 SOM。

让我们从SAMA5D27 SiP开始,它采用32位ARM Cortex-A5微控制器,128Mb、512Mb或1Gb DDR2内存。该SiP可以用作独立器件,也可以集成到更大的组件中,如SAMA5D27 SOM。

除了SAMA5D27 SiP之外,SAMA5D27 SOM还包含64Mb QSPI闪存器件、2Kb EEPROM芯片(带有预编程MAC地址),带时钟的10/100以太网PHY、一个高性能电源管理IC(MIC2800)和103个输入/输出(I/O)。使用SAMA5D27 SOM的结果是缩小印刷电路板的尺寸和层数,将设计风险降至最低,并大大缩短产品开发时间。

结论

唉!我不知道你怎么想,但我的脑子里真的是一片混乱。在上世纪70年代末,事情往往简单得多,那时我们只需要担心与TI公司的7400系列器件相关联的双列直插式(DIL)封装。

当然,如果我们试图用过去的技术实现像智能手机一样的东西,它将会有牵引式卡车那么大。当今的ASIC/ASSP/SoC技术与SiP、PiP、PoP、MCM、CoM和SoM封装/部署技术相结合,使我们所熟悉和喜爱的高密度、高性能系统成为可能。